# CPCI-CAN/400-CC

4x CAN (Layer 2, CANopen<sup>®</sup>, J1939 or ARINC 825), Conduction Cooled with Bus Master DMA

# 4 High-Speed CAN Interfaces for CompactPCI<sup>®</sup> with Bus Master DMA

- CAN interfaces according to ISO 11898-1

Capable of 100% CAN bus load

- Capable of 100% CAN bus load

Reduces system load by bus master DMA transfer

- Enhanced diagnostic features

- e.g. CAN error injection

- 33/66 MHz CompactPCI interface

#### Realtime OS Drivers, J1939 and ARINC825 Higher Layer Protocol Support

- Drivers and higher layer protocols for Windows<sup>®</sup>, Linux<sup>®</sup>, VxWorks<sup>®</sup>, QNX<sup>®</sup>, RTX, On Time RTOS-32 and others

- CANopen, J1939 and ARINC 825 protocol available

- CAN is driven by approved esd Advanced CAN Core (esdACC) CAN controller

# **Conduction Cooled Design**

- Conduction cooled 3U format, IEEE1101.2 compliant

- All I/O-signals connected via CompactPCI connector P2

### CPCI CAN Interface

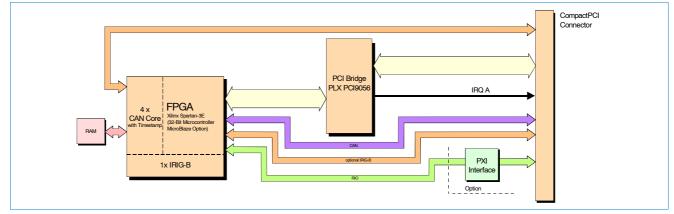

The CPCI-CAN/400-CC is a CompactPCI board in conduction cooled 3U format, that features four CAN High-Speed interfaces according to ISO 11898-1. CAN is driven by the esdACC (esd Advanced CAN Core) implemented in the Xilinx Spartan 3e FPGA. The CPCI CAN/400 CC provides high

The CPCI-CAN/400-CC provides high resolution hardware timestamps.

#### Connectivity

All I/Os are connected to P2 connector.

# Software Support<sup>1</sup>

Operating system independent CAN layer 2 API (NTCAN).

- Multiple Higher Level Protocols available

- CANopen Master- and Slave-Stack

- J1939 (Windows only)

- ARINC825

# Options PXI and µC

The CPCI-CAN-400-CC optionally features a PXI interface:

The signals TRG 0-7, CLK 10 and STAR are controlled via the FPGA. The signals LBL/LBR1-12 are looped through.

An optional 32-bit MicroBlaze  $\mu C$  is available in the FPGA. Please, contact our sales team (sales@esd.eu) for further information.

(This product is under development. It will be available Q1 2014.)

#### Technical Specifications:

CompactPCI Interface and Microprocessor:

| CompactPCI In  | terrace and Microprocessor:                                                                                                   |

|----------------|-------------------------------------------------------------------------------------------------------------------------------|

| Interface      | PCI bus according to PCI Local Bus<br>Specification 2.2, 32 bit 33/66 MHz,<br>3.3 V (5 V tolerant), bus master DMA capability |

| Memory         | BlockRAM: 72 KB, DRAM: 64 MB                                                                                                  |

| CAN:           |                                                                                                                               |

| Interface      | 4x CAN high-speed interface LVTTL,<br>bit rate up to 1 Mbit/s                                                                 |

| CAN controller | According to ISO 11898-1 (CAN 2.0 A/B)                                                                                        |

| General:       |                                                                                                                               |

| Ambient temp.  | -40 °C+75 °C, conduction cooled in compliance<br>with IEEE 1101.2                                                             |

| Rel. humidity  | Max. 90 %, non-condensing                                                                                                     |

| Connectors     | P1, P2                                                                                                                        |

| Power supply   | 5 V, $I_{sv}$ = 185 mA (typical)<br>3.3 V, $I_{3.3v}$ = 265 mA (typical)                                                      |

|                |                                                                                                                               |

| Order Information:                                                  |           |  |

|---------------------------------------------------------------------|-----------|--|

| Hardware                                                            | Order No. |  |

| CPCI-CAN/400-CC 4x CAN via P2 (LVTTL-Level)                         | C.2034.05 |  |

| CAN layer 2 drivers for Windows and Linux are included in delivery. |           |  |

| Software Support                                                    |           |  |

| CAN layer 2 object licences including CD-ROM <sup>1</sup> :         |           |  |

| CAN-DRV-LCD QNX                                                     | C.1101.32 |  |

| CAN-DRV-LCD VxWorks                                                 | C.1101.55 |  |

| CAN-DRV-LCD RTX                                                     | C.1101.35 |  |

| CAN-DRV-LCD OnTime-RTOS-32                                          | C.1101.45 |  |

| Higher layer protocols <sup>1</sup> :                               |           |  |

| CANopen-LCD Windows/Linux                                           | C.1101.06 |  |

| CANopen-LCD QNX                                                     | C.1101.17 |  |

| CANopen-LCD VxWorks                                                 | C.1101.18 |  |

| CANopen-LCD RTX                                                     | C.1101.16 |  |

| J1939stack for Windows                                              | C.1130.10 |  |

| J1939 stack for Linux                                               | C.1130.11 |  |

| ARINC825-LCD Windows / Linux                                        | C.1140.06 |  |

| ARINC825-LCD QNX                                                    | C.1140.17 |  |

| ARINC825-LCD VxWorks                                                | C.1140.18 |  |

| ARINC825-LCD RTX                                                    | C.1140.16 |  |

<sup>1</sup> For detailed information about the driver availability of your special operating system please contact our sales team.

©2014 esd electronic system design gmbh Hannover All data are subject to change without prior notice. I:TextelDoku/DBL\CPCIEnglischBlue\CPCI-CAN400-CC\_Datasheet\_en\_20.wpd

CANopen® and CiA® are registered Community Trademarks of CAN in Automation e.V.. All other trademarks are reserved by their respective owners.

esd electronic system design gmbh Vahrenwalder Str. 207 30165 Hannover / Germany

# **CPCI-CAN/400-CC** Driven by esdACC (Advanced CAN Core)

# Basic Product Features:

- CAN ISO 11898-1 protocol compatibility

- 11-bit and 29-bit CAN IDs

- Bit rates from 10 kbit/s up to 1 Mbit/s supported

- Receive buffer (64 CAN messages)

- Complete access to CAN error counters

- Programmable error warning limit

- Error code capture register

- · Error interrupt for each CAN bus error

- Arbitration lost interrupt with detailed bit position

- Single-shot transmission (no re-transmission)

- Listen only mode (no acknowledge, no active error flags)

- Automatic bit rate detection (software supported bit rate detection)

- Acceptance filter (4-byte code, 4-byte mask)

- Self reception mode (reception of 'own' messages)

#### Superior esdACC Features:

- Operating system independently programmable via esd's NTCAN-API

- 32-bit register interface optimized for CAN needs

- Easy to program

- Transmission and reception of CAN frames with a minimum of register accesses

- RX and TX timestamping (64-bit wide, bit accurate, resolution may

vary with input clock, in any case ≤ 62.5 ns, usually 20.833 ns)

On hardware with IRIG-B interfaces IRIG-B time is used for timestamping

- TX FIFO (8 CAN frames deep)

- Providing the means to generate 100% busload even with non-realtime operating systems

- Providing the means for real back-to-back transmission

- Frame accurate abortion of transmissions with minimum delay

- e.g. for driver timeouts

- ISO11898-1 conform

- Aborted frames in FIFO won't be blocked by low priority TX

- Hardware timer to provide accurate software timeouts beyond operating system accuracy

- Bus mastering in RX direction takes the load off host CPU (needs bus master capable local bus to host interface)

- Optional integration with 32-bit microcontroller to further relieve host CPU

- Optional different sources for timestamps (e.g. IRIG-B)

- CAN error injection units

- Simulating a wide range of error situations on CAN bus, e.g.:

- ID pollution (100% bus load on certain CAN ID/priority)

Defective sensor (Destroying all CAN messages of a given CAN ID)

- Different trigger modes

- Bit pattern match

- Time triggered

- Immediate regarding CAN arbitration

- External

- 'Cross CAN bus triggering'

- (event on one CAN bus triggers event on another bus)

- Using FPGA technology provides the option to tailor any feature to any customer's needs, including optional integration with customer's FPGA content

- The esdACC IP core has been verified on Xilinx Spartan and Altera Cyclone FPGAs.

©2014 esd electronic system design gmbh Hannover esdACC-DBL-text\_segment\_en\_10.wpd All data are subject to change without prior notice.

esd electronic system design gmbh Vahrenwalder Str. 207 30165 Hannover / Germany

# Driver Availability:

Windows, Linux<sup>1</sup>, QNX<sup>1</sup>, VxWorks<sup>1</sup>, RTX<sup>1</sup>

CANopen<sup>®</sup> and CiA<sup>®</sup> are registered Community Trademarks of CAN in Automation e.V.. All other trademarks are reserved by their respective owners. Phone: +49 (0) 511 3 72 98-0

Email: info@esd.eu

Fax:

+49 (0) 511 3 72 98-68

<sup>1</sup> For detailed information about the driver availability for your operating system and the particular esd CAN interface please contact our sales team.

#### Available Higher Level Protocols:

#### CANopen, ARINC825, J1939

For further information on the esdACC IP Core please contact our sales team.

Availability of the superior esdACC features depends on the operating system and the hardware. Please contact our sales team for further information.